# Paper

SAMPL Lab

# Practical Modulo Sampling: Bridging the Gap Between Theory and Hardware

Yhonatan Kvich, Shlomi Savariego, Moshe Namer, Yonina C. Eldar

Faculty of Mathematics and Computer Science, Weizmann Institute of Science, Rehovot, Israel

### 1. Motivation and Contributions

- > ADCs play a crucial role in digital signal processing, demanding a dynamic range (DR) greater than the input signal to avoid information loss.

- > While sampling is fundamental to ADC performance, higher rates lead to increased costs and complexity.

- > Leveraging the modulo operator enables the development of ADCs with extended DR while operating at lower sampling rates, effectively addressing the DR challenge.

#### Our contributions are twofold:

- > We have developed hardware capable of performing modulo operations on signals up to 10 kHz, utilizing an ADC with a bandwidth equal to the sampling rate of 50 kHz.

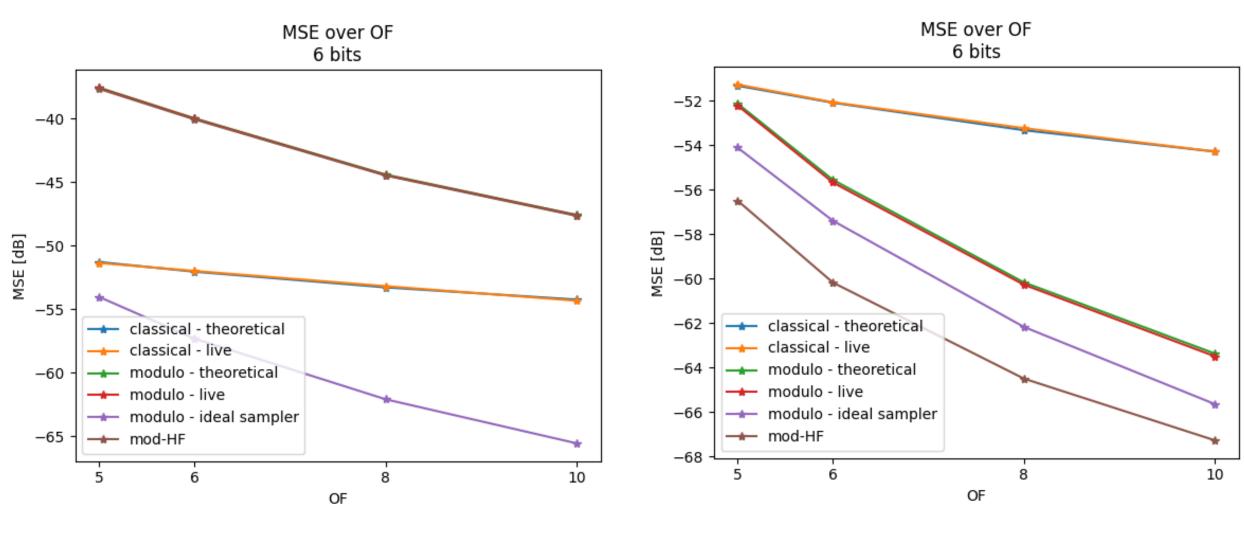

- > Through simulations and hardware tests, our approach has demonstrated superior noise resilience and efficiency compared to existing methods, making it a viable sampler for realworld applications.

The design efficiently handles high-frequency components from the modulo operation, ensuring **practicality for real-world use**.

It reduces quantization error with the same bit budget, outperforming conventional samplers in accuracy and efficiency.

# 2. Problem Statement

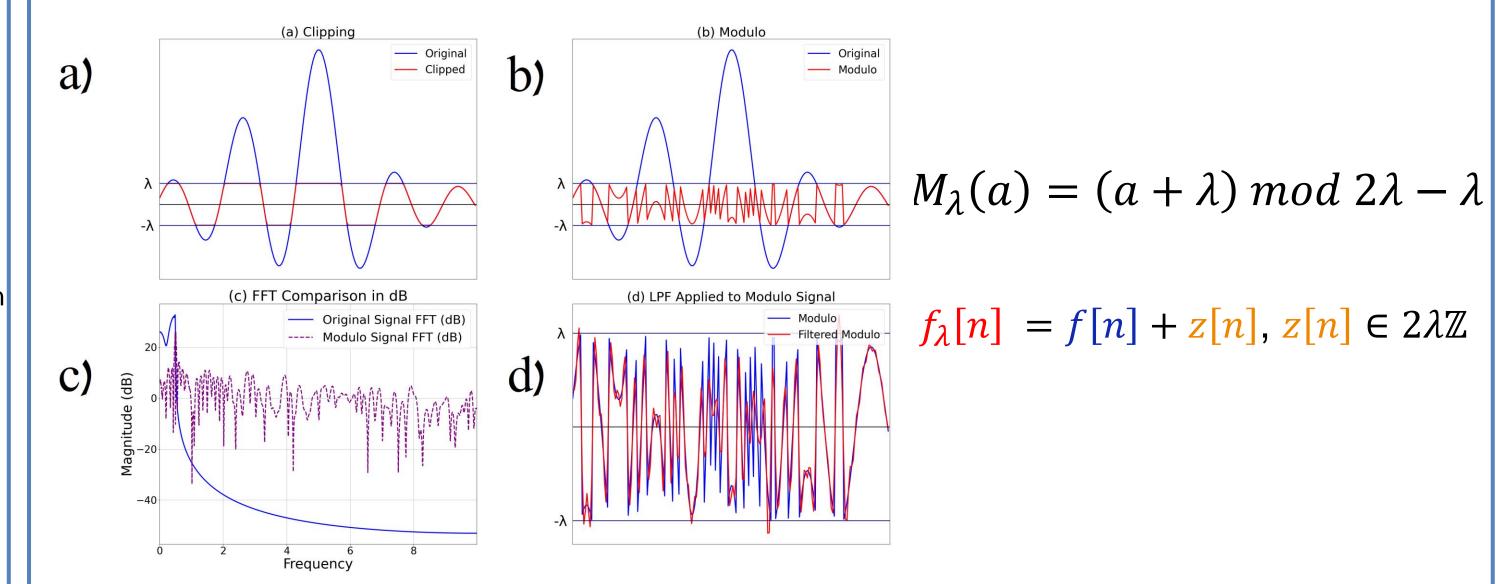

# > Modulo Sampling:

- > Modulo operations introduce high-frequency components, complicating recovery.

- > Low-pass filters (LPF) remove critical frequencies, causing information loss.

- > Existing methods cannot effectively handle challenges from modulo operations and LPF effects.

- > Higher bandwidths require more powerful ADCs, increasing cost and complexity.

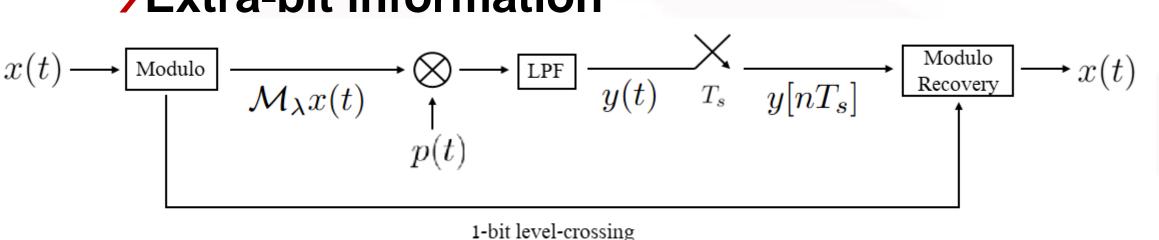

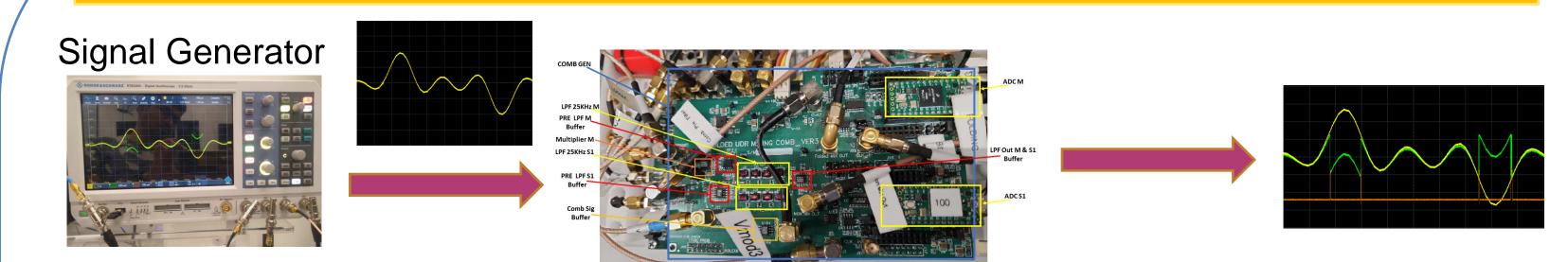

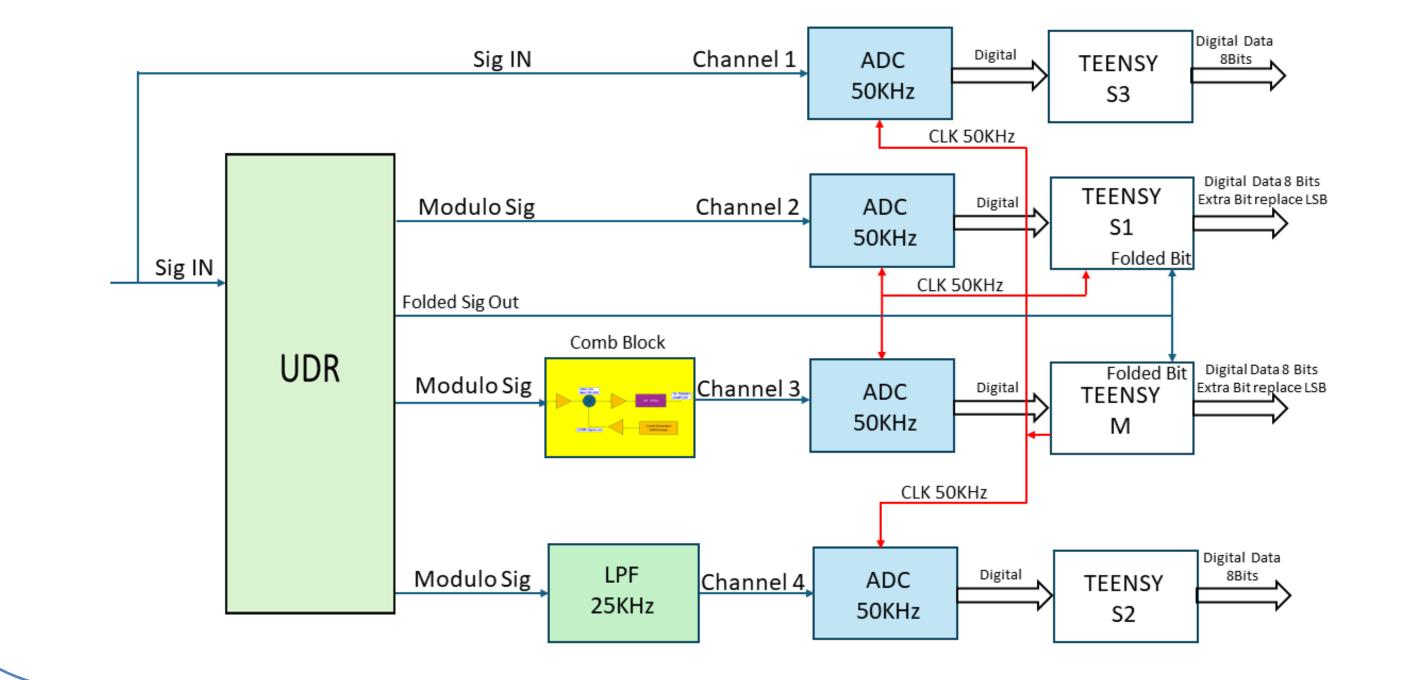

# 3. Practical Sampling System

- >Use of mixer and LPF

- >Extra-bit information

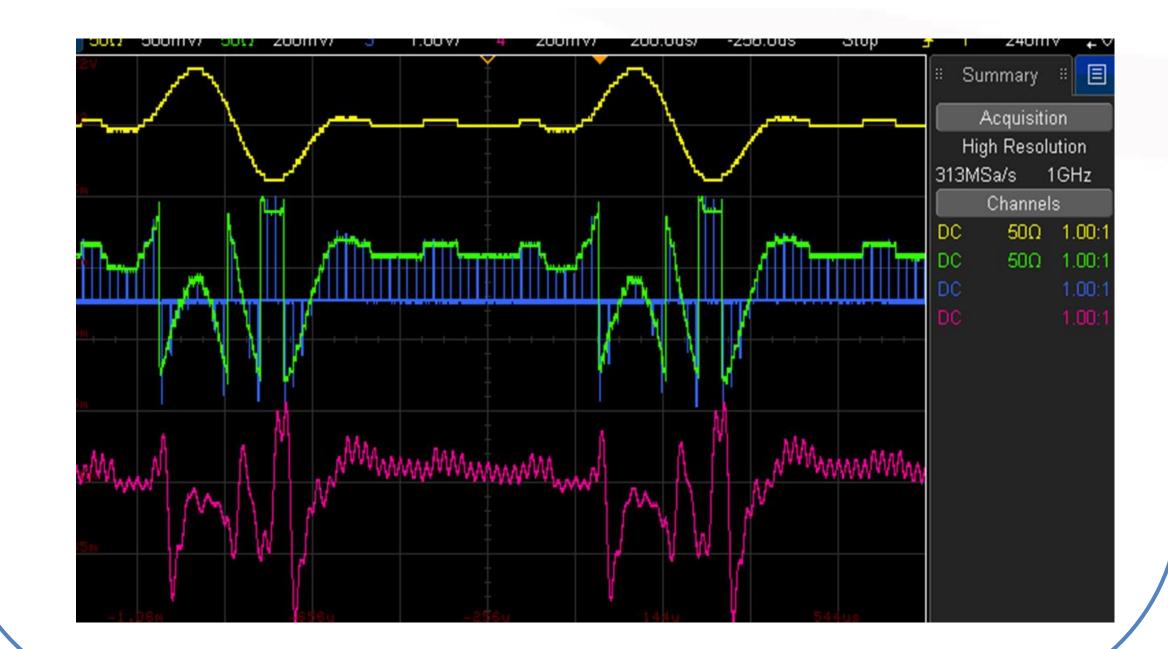

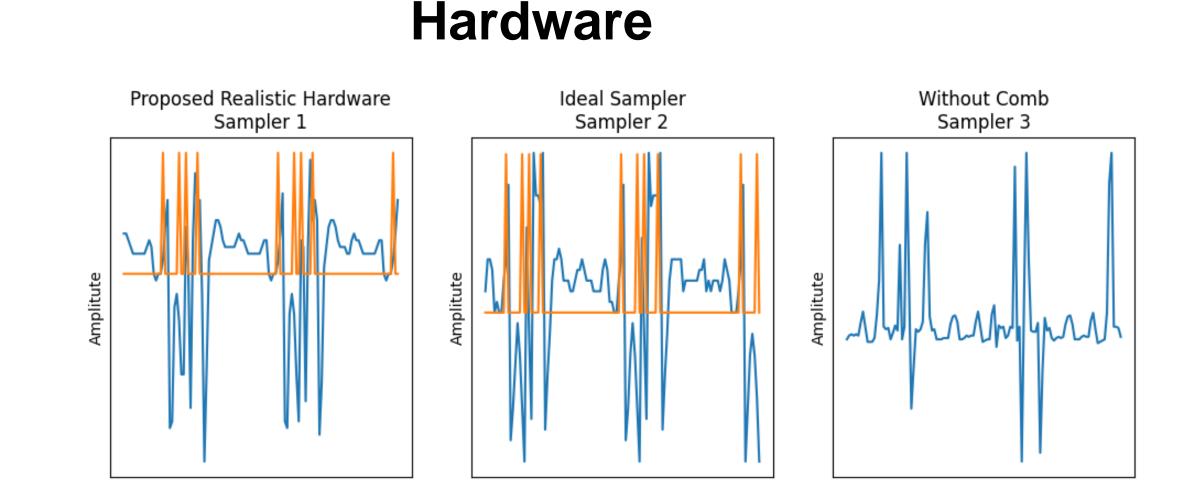

## 4. Hardware

- > Comparators generate a trigger signal whenever the input signal exceeds the ADC's DR.

- > The trigger activates a voltage generator, which adjusts the input signal to keep it within the DR.

#### Simulation

#### Conclusion

- > Modulo sampling generates high-frequency components.

- Current methods depend on high-rate ADCs to capture the frequencies.

- Our approach offers a practical hardware solution to addre these challenges efficiently.

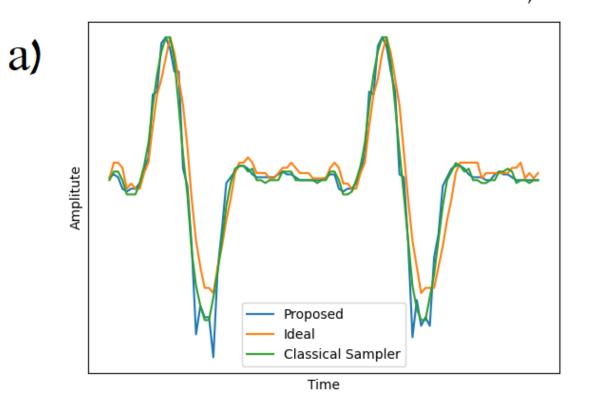

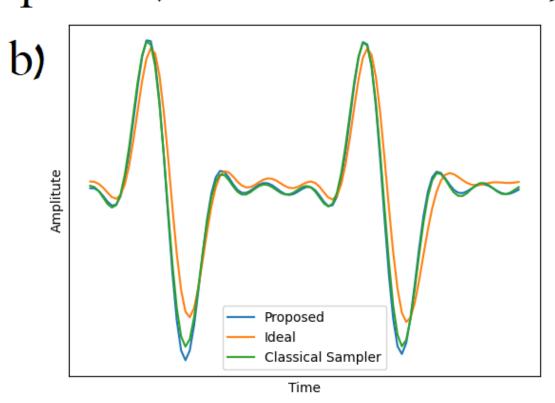

# 5. Results

Recovered Signals Comparison

Ideal (ADC Band 20 MHz), Proposed (ADC Band 50 KHz)